東京大学生造技術研究所 REDUCTION CONTRACTOR CONTRACTOR OF CONTRAC

# HIRAMOTO LAB

# [Silicon Nanotechnology and VLSI Devices]

Department of Informatics and Electronics

http://vlsi.iis.u-tokyo.ac.jp

# Integrated Device Engineering

Department of Electrical Engineering and Information Systems

## **Background and Targets**

#### **CMOS Technology in Future**

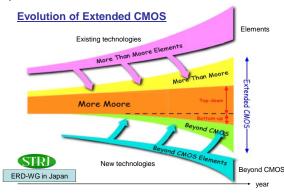

Our vision for future CMOS technology is shown below. Socalled Beyond CMOS devices will be merged into CMOS platform to form ultimate "Extended CMOS".

#### Approaches to the Targets

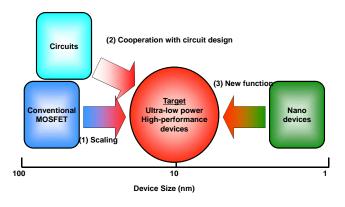

We adopt three approaches to the targeted ultra-fast low-power ultimate CMOS devices.

## Main Achievements

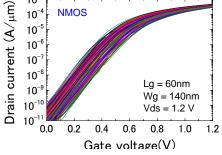

#### Characteristics Variability in Scaled CMOS Transistor variability, one of the most serious problem in VLSI, is

addressed and its suppression method is pursued.  $10^{-3}$

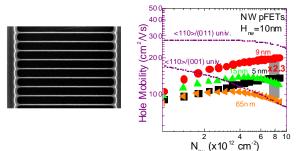

#### Silicon Nanowire Transistor

Silicon nanowire transistor is promising for future VLSI. Mobility enhancement in silicon nanowire transistors has been experimentally demonstrated for the first time.

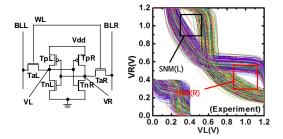

**SRAM Instability**

SRAM, a memory for logic circuits, is easily affected by variability. In our lab, the butterfly curves of SRAM cells can be directly measured.

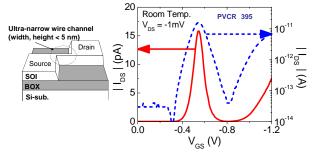

#### Silicon Single-Electron Transistor

Single-electron transistor is an ultimate electron device. We observed record high peak-to-valley ratio in a silicon single-electron transistor at room temperature.